-

开放科学(资源服务)标志码(OSID):

-

TSV(Through Silicon Via,硅通孔)是目前三维芯片封装中实现多层芯片垂直互连功能的关键技术[1-2],TSV是在不同的芯片间刻蚀垂直方向上互通的通孔,并向通孔中淀积金属来实现芯片间电学互连[3-4],和以前的封装技术不同,TSV技术可以实现在垂直方向堆叠多层芯片,从而极大地提高芯片的堆叠密度,大大缩小尺寸,并且可以极大地提高芯片的运行速度和降低功耗[5-6].

随着微电子技术的不断发展,集成电路的集成度不断提高,封装技术也在朝着高集成度、三维封装方向发展[7],其中TSV技术的三维封装是先进封装技术的前沿和热点之一,基于TSV技术的三维封装具有高集成度、高性能、低功耗等特点,但也存在着很多的挑战. 由于封装系统内各种材料的热膨胀系数存在较大差异以及热传导系数各不相同,在焦耳热的影响下,会在封装系统内部产生热应力,这种热应力会引起芯片局部的断裂和芯片的翘曲[8],由于引入TSV结构而引起的热应力、形变等问题是TSV技术最主要的挑战,而利用仿真软件模拟可以很好地帮助研究芯片的热应力和微加工问题[9-12].

除了芯片层间连接可使用TSV技术,芯片与芯片基板之间也可以使用TSV技术进行连接. 在众多基板材料中,低温共烧陶瓷(Low Temperature Co-fired Ceramic,LTCC)以其优异的封装性能和介电性能,在无线通信设备中得到了广泛的应用[13-14]. LTCC基板可以提高布线密度和信号传输速度,其热膨胀系数可以做到和硅器件接近,对安装裸片硅器件非常有利,且可以内埋无源元件,形成立体高密度组件[15]. 本文研究的三维芯片采用的是以LTCC为基板,使用TSV技术实现芯片间及芯片与基板之间的互联,TSV中的填充金属使用的是锡铅银合金.

本研究利用仿真软件对TSV芯片在高温工作下的热应力及应变进行了仿真分析,模拟应力与实测应力之间的差异主要是受残余应力的影响[16],通过对室温下残余应力测量值的补偿,模拟得到的径向和轴向热应力与实测数据吻合较好,验证了模拟方法的有效性. 通过设计4种不同TSV数量和分布的模型,对芯片的热应力和应变进行仿真分析,对比仿真的结果,找出较为优化的参数设计.

HTML

-

本文研究的三维芯片采用的是以LTCC为基板的三维堆叠芯片,并使用TSV技术实现芯片间及芯片与基板之间的互联.

TSV中填充金属使用的是62.5Sn37Pb0.5Ag,锡铅共晶或近共晶钎料熔点较低,在对通孔进行填充时,可以有效降低加工温度,提高芯片的良品率. 由于加工时温度相对较低,也可以使芯片在堆叠后再进行填充,使芯片间具有更好的连接性,在锡铅合金中加入少量Ag可以提高锡铅合金的蠕变寿命.

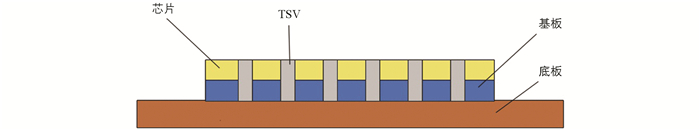

器件结构如图 1所示,器件是由TSV芯片、基板及底板构成,TSV所构成的通孔贯穿芯片与基板,并在通孔中填充金属材料. 在这个模型中,TSV芯片是正方体,其边长为5 mm,芯片的厚度是100 μm,基板使用LTCC,厚度为100 μm,TSV的直径为250 μm. 基板下的底板辅助模拟器件装载在电路板时的散热.

-

运用COMSOL传热中的热应力研究模块对此器件的结构进行热应力仿真,三维模型如图 2所示.

仿真做如下设置:①忽略Ti/W阻挡层和Cu种子层. ②忽略基板对TSV热应力及应变的影响. ③芯片四角设置了导角,降低计算误差. ④忽略了封装过程中的残余应力和应变. 在实际情况中,对于封装体的不同区域与材料,其对应的零应力温度是不相同的,为了简便起见,在建模仿真的过程中,将封装体的零应力温度设定为25 ℃.

为了研究该模型下TSV在芯片不同位置的热应力以及不同分布及数量对TSV芯片热应力的影响,该研究建立了4种模型进行对比分析. 第一种模型:TSV芯片内均匀分布6×6个通孔,通孔与通孔之间的距离及通孔至芯片外侧的距离相等. 第二种模型:TSV芯片内均匀分布4×4个通孔,其分布方式也为均匀分布. 通过对第一、二种模型进行对比分析,研究通孔在均匀分布下,通孔的数量及孔间距离对TSV芯片热应力的影响. 第三种模型:TSV芯片内分布4×4个通孔,通孔分布在芯片中心,通孔与芯片外侧距离较大,通孔之间的距离与第一种模型相等,主要研究分布在芯片中心的通孔对TSV芯片的热应力的影响. 第四种模型:TSV芯片有20个通孔,通孔之间的距离与第一种模型相等,均匀分布在芯片外侧,主要研究分布在芯片外侧的通孔对TSV芯片的热应力的影响.

-

TSV芯片使用单晶硅,其热膨胀系数为2.6×10-6 K-1,恒压热容为700 J/(kg·K),密度为2 329 kg/m3,杨氏模量为170 GPa,泊松比为0.28.

单晶硅的导热系数较高为131 W/(m·K),但在实际使用时,芯片的散热不只是受单晶硅的导热系数影响,散热也会受到单晶硅外的二氧化硅绝缘层及外部封装影响,所以在计算时,将芯片的导热系数设为1.38 W/(m·K).

基板使用LTCC,其热膨胀系数为7×10-6 K-1,恒压热容为900 J/(kg·K),密度为2.5 kg/m3,导热系数为2 W/(m·K),杨氏模量为85 GPa,泊松比为0.28.

填充金属使用62.5Sn37Pb0.5Ag,锡铅银合金在不同温度时,其材料属性也会有变化,在20 ℃时. 热膨胀系数为2.4×10-5 K-1,恒压热容为188 J/(kg·K),密度为8 400 kg/m3,导热系数为50 W/(m·K),杨氏模量为42.1 GPa,泊松比为0.4.

-

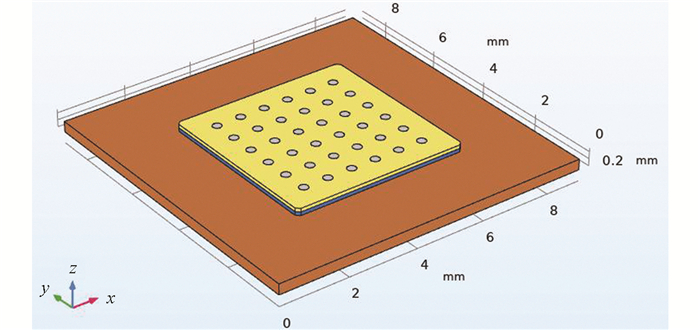

为了提高运算速率,设置最大单元格为0.18,曲率因子为0.2,最大单元增长率为1.3. 而在部分TSV设置的最大单元格为0.08,曲率因子为0.1,以得到更多的计算结果数据而方便分析,网格划分如图 3.

-

为了获得TSV稳态下的热应力,需对三维仿真模型中的热传导方程及热应力方程进行联立求解[17],在此三维仿真模型中,热传导稳态求解方程为

模型与外部环境采用对流热通量进行计算,方程为

其中h是导热系数,Text是外部环境温度.

在此模型中,芯片模拟为均匀发热,热源直接由热耗率计算热通量:

其中V为芯片体积,P0为热损耗功率.

根据Hook定律,此模型稳态时热应力方程为

其中f为体积力,σ是热应力张量,ε是总应变,εTh是热应变,u为位移,C为单元刚度矩阵. α(T)=Σn=04anTn是随温度变化的热膨胀系数,an通过曲线拟合可以得到[18],Tref为体积参考温度. 在本研究中不考虑材料的塑形形变[19],通过Neumann边界条件和Dirichlet边界条件,利用共轭梯度法和逐单元近似分解法求解耦合温度场和热应力场. 在COMSOL多物理场仿真中也包含计算方法,可以直接调用软件中内部算法配置进行仿真计算.

2.1. 模型设置

2.2. 材料属性定义

2.3. 网格划分

2.4. 数值计算方法

-

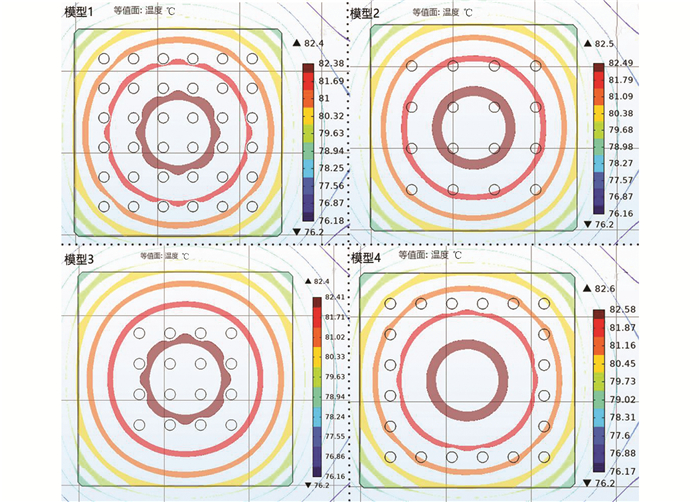

运用COMSOL传热中的热应力研究模块对设计的结构进行热应力仿真,使用稳态分析. TSV芯片的等温线分布如图 4所示,可以看出热源区域最高温度为82 ℃,芯片边缘温度为79 ℃,芯片中间区域的温度最高,从芯片中心到外围温度逐渐降低,形成这样的温度分布的原因是由于硅外层覆盖的绝缘层和封装的导热系数相对较低,芯片越靠近外侧,表面积与体积的比值越大,芯片外侧能够更好的散热,因此,若考虑热辐射计算,温度分布将更明显.

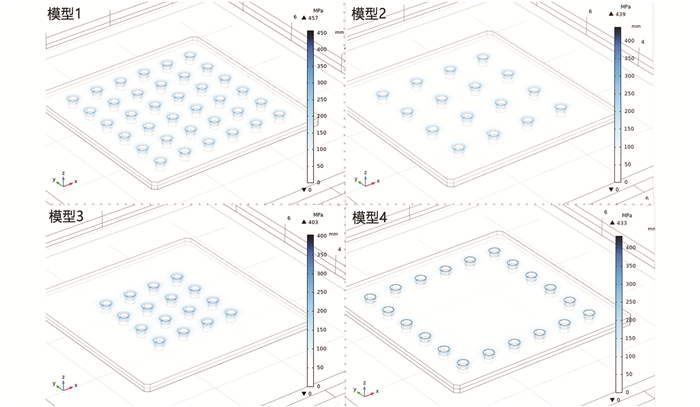

设置形变放大倍数100倍,芯片的应力分布如图 5所示. 从芯片的应力分布图可以看出,每个TSV的最大应力分布位置都相同,应力主要分布在TSV的外侧,应力分布与TSV的位置相关性不大,但是越靠近芯片内侧的通孔,最大应力会有所减小.

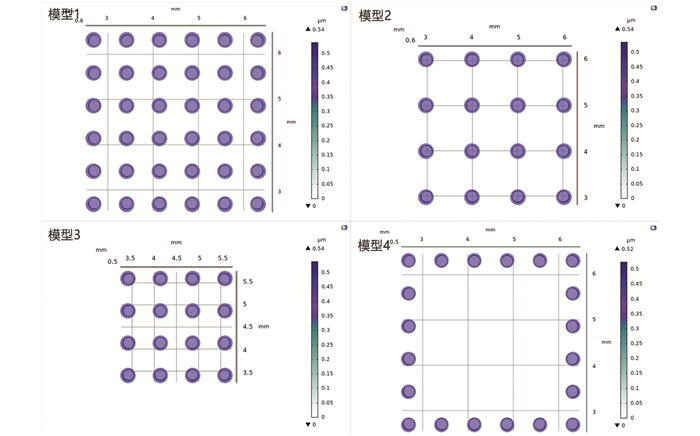

填充金属的形变放大400倍后的俯视图如图 6所示. 从图中可以看出,填充金属的形变位移方向是从芯片中心向外,形成这样的位移方向主要是受到芯片热膨胀形变的影响,芯片热膨胀导致了形变位移的累计,越靠近芯片外侧累积的形变位移越大,因此填充金属越靠近芯片外侧,会受到芯片更大的形变影响. 从图 5可以看出,由于芯片变形的累积影响,导致越靠近芯片外侧的TSV的应力也会越大.

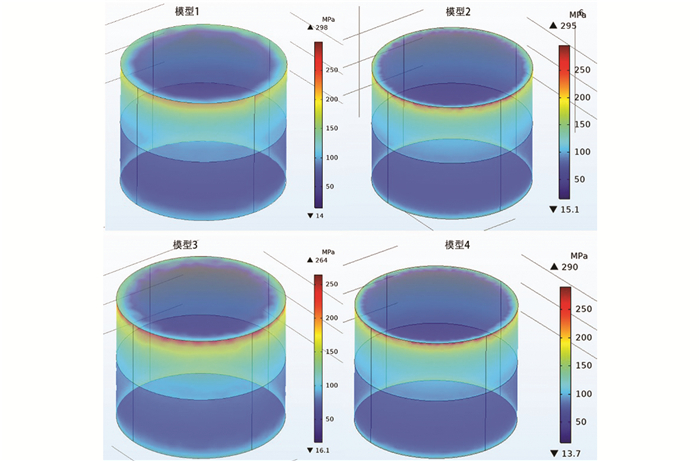

观察其中一种模型的通孔,填充金属表面的应力分布如图 7所示,TSV的最大应力主要分布在通孔上侧,通孔内部受到应力相对均匀,单晶硅与LTCC基板的交界处有明显的应力变化,但变化值不大.

再观察其中一个模型的通孔,将形变放大200倍,形变与应力分布截面图如图 8所示. 由于锡铅银合金的热膨胀系数相较于单晶硅和LTCC基板较大,芯片在受热后,TSV内的通孔无法容纳锡铅银合金的体积,锡铅银合金通过通孔向外挤出,导致TSV外侧受到较大的应力. 由于LTCC基板与单晶硅的膨胀系数接近,因此在LTCC与单晶硅的交界处没有明显的应力分布.

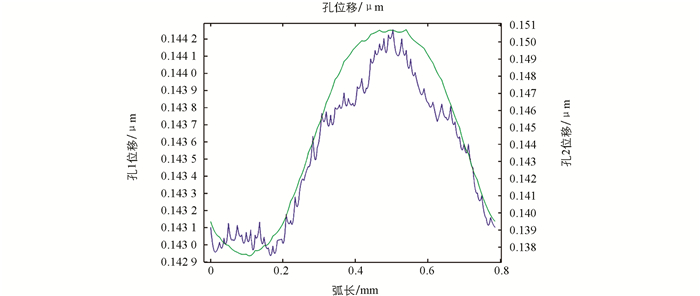

在第一个模型上,分别取芯片对角线上最外侧孔2与其向内的一个通孔1在TSV芯片与基板交界处的位移如图 9所示. 在单晶硅与LTCC基板的交界处,形变位移的方向相同,且靠近芯片外侧的通孔2具有更大的形变位移,说明越靠近芯片外侧的通孔,其形变越大.

-

从实验仿真中可以看出,由于LTCC与单晶硅结晶的热膨胀系数相近,以LTCC作为TSV芯片基板,芯片在高温工作时,TSV在单晶硅与LTCC的交界处不会产生较大形变差异. TSV芯片所受应力主要集中在TSV外侧,其主要原因是由于填充金属受热膨胀影响被挤出通孔,造成TSV外侧受到挤压. 设计TSV时需要考虑使用其他材料或工艺强化通孔外侧的强度,或在单晶硅与通孔之间设置一层柔性材料,使填充金属在形变后不会产生太大的应力.

对4种仿真模型的热应力分布进行对比分析可以得出,TSV的分布对TSV芯片的应变影响较大,其主要原因是由于芯片形变位移的累计效应. TSV的分布越靠近芯片内侧,其表面应力则会越小,且TSV芯片与LTCC基板之间的相对位移也小,在设计TSV位置时,可以尽可能将TSV设置在芯片中心,以降低由于芯片与基板之间的位移造成填充金属的断裂失效.

DownLoad:

DownLoad: